# MAR GREGORIOS COLLEGE OF ARTS & SCIENCE

Block No.8, College Road, Mogappair West, Chennai – 37

Affiliated to the University of Madras Approved by the Government of Tamil Nadu An ISO 9001:2015 Certified Institution

# **DEPARTMENT OF**

# **COMPUTER SCIENCE**

SUBJECT NAME: COMPUTER ORGANIZATION

**SUBJECT CODE: SE22A**

**SEMESTER: II**

**PREPARED BY: PROF. C.SUJDHA**

#### UNIT - I

Data representation: Data types – Complements- fixed point and floating point representation other binary codes. Register Transfer and Microoperations: Register transfer language- Register transfer- Bus and Memory transfers – Arithmetic, logic and shift micro operations.

#### **Data Representation:Data type**

- Registers contain either data or controlinformation

- Control information is a bit or group of bits used to specify the sequence of command signals needed for data manipulation

- Data are numbers and other binary-coded information that are operatedon

- Possible data types inregisters:

- Numbers used incomputations

- Letters of the alphabet used in dataprocessing

- Other discrete symbols used for specific purposes

- All types of data, except binary numbers, are represented in binary-codedform

- A number system of *base*, or *radix*, *r* is a system that uses distinct symbols for *r* digits

- Numbers are represented by a string of digitsymbols

- The string of digits 724.5 represents thequantity

$$7 \times 10^2 + 2 \times 10^1 + 4 \times 10^0 + 5 \times 10^{-1}$$

• The string of digits 101101 in the binary number system represents thequantity

$$1 x 2^{5} + 0 x 2^{4} + 1 x 2^{3} + 1 x 2^{2} + 0 x 2^{1} + 1 x 2^{0} = 45$$

- $(101101)_2 = (45)_{10}$

- We will also use the octal (radix 8) and hexidecimal (radix 16) numbersystems

$(736.4)_8 = 7 \times 8^2 + 3 \times 8^1 + 6 \times 8^0 + 4 \times 8^{-1} = (478.5)_{10}$

$$(F3)_{16} = F \times 16^1 + 3 \times 16^0 = (243)_{10}$$

- Conversion from decimal to radix *r* system is carried out by separating the number into its integer and fraction parts and converting each partseparately

- Divide the integer successively by *r* and accumulate theremainders

- Multiply the fraction successively by *r* until the fraction becomeszero

| eger = 41             | Fraction = 0.6875            |

|-----------------------|------------------------------|

| 1                     | 0.6875                       |

| 1                     | 2                            |

| 0                     | 1.3750                       |

| 0                     | x 2                          |

| 1                     | 0.7500                       |

| 0                     | x 2                          |

| 1                     | 1.5000                       |

|                       | x 2                          |

|                       | 1.0000                       |

| $)_{10} = (101001)_2$ | $(0.6875)_{10} = (0.1011)_2$ |

| $(41.6875)_{10} = ($  | 101001.1011) <sub>2</sub>    |

|                       |                              |

Figure 3-1 Conversion of decimal 41.6875 into binary.

- Each octal digit corresponds to three binarydigits

- Each hexadecimal digit corresponds to four binarydigits

- Rather than specifying numbers in binary form, refer to them in octal or hexadecimal and reduce the number of digits by 1/3 or <sup>1</sup>/<sub>4</sub>, respectively

| 1 | _ | 2 | _ | _ | 7 | _ | _ | 5 | _ | _ | 4 | _ | - | 3 | _ | Octal       |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|-------------|

| 1 | 0 | 1 | 0 | 1 | 1 | 1 | 1 | 0 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | Binary      |

|   | 1 | 4 |   |   | F |   |   |   | ( | 5 |   |   | 1 | 3 |   | Hexadecimal |

Figure 3-2 Binary, octal, and hexadecimal conversion.

#### TABLE 3-1 Binary-Coded Octal Numbers

|         | Decimal equivalent | Binary-coded<br>octal | Octal<br>number |

|---------|--------------------|-----------------------|-----------------|

| Î       | 0                  | 000                   | 0               |

| 1       | 1                  | 001                   | 1               |

| Code    | 2                  | 010                   | 2               |

| for one | 3                  | 011                   | 3               |

| octal   | 4                  | 100                   | 4               |

| digit   | 5                  | 101                   | 5               |

| 1       | 6                  | 110                   | 6               |

| 1.      | 7                  | 111                   | 7               |

|         | 8                  | 001 000               | 10              |

|         | 9                  | 001 001               | 11              |

|         | 10                 | 001 010               | 12              |

|         | 20                 | 010 100               | 24              |

|         | 50                 | 110 010               | 62              |

|         | 99                 | 001 100 011           | 143             |

|         | 248                | 011 111 000           | 370             |

| Hexadecimal number | Binary-coded<br>hexadecimal | Decimal equivalent |             |

|--------------------|-----------------------------|--------------------|-------------|

| 0                  | 0000                        | 0                  | 1           |

| 1                  | 0001                        | 1                  |             |

| 2                  | 0010                        | 2                  | 1           |

| 3                  | 0011                        | 3                  |             |

| 4                  | 0100                        | 4                  | 1           |

| 4<br>5             | 0101                        | 5                  |             |

| 6                  | 0110                        | 6                  | Code        |

| 7                  | 0111                        | 7                  | for one     |

| 8                  | 1000                        | 8                  | hexadecimal |

| 9                  | 1001                        | 9                  | digit       |

| Α                  | 1010                        | 10                 |             |

| В                  | 1011                        | 11                 |             |

| С                  | 1100                        | 12                 |             |

| D                  | 1101                        | 13                 |             |

| E                  | 1110                        | 14                 | *           |

| F                  | 1111                        | 15                 | Ļ           |

| 14                 | 0001 0100                   | 20                 |             |

| 32                 | 0011 0010                   | 50                 |             |

| 63                 | 0110 0011                   | 99                 |             |

| F8                 | 1111 1000                   | 248                |             |

TABLE 3-2 Binary-Coded Hexadecimal Numbers

- A binary code is a group of n bits that assume up to  $2^n$  distinct combinations

- A four bit code is necessary to represent the ten decimal digits 6 areunused

- The most popular decimal code is called *binary-coded decimal*(BCD)

- BCD is different from converting a decimal number tobinary

- For example 99, when converted to binary, is1100011

- 99 when represented in BCD is 10011001

|         | Binary-coded decimal<br>(BCD) number | Decimal<br>number |

|---------|--------------------------------------|-------------------|

| 1       | 0000                                 | 0                 |

|         | 0001                                 | 1                 |

|         | 0010                                 | 2                 |

| Code    | 0011                                 | 3                 |

| for one | 0100                                 | 4                 |

| decimal | 0101                                 | 5                 |

| digit   | 0110                                 | 6                 |

|         | 0111                                 | 7                 |

|         | 1000                                 | 8                 |

| Ļ       | 1001                                 | 9                 |

|         | 0001 0000                            | 10                |

|         | 0010 0000                            | 20                |

|         | 0101 0000                            | 50                |

|         | 1001 1001                            | 99                |

|         | 0010 0100 1000                       | 248               |

TABLE 3-3 Binary-Coded Decimal (BCD) Numbers

- The standard alphanumeric binary code is ASCII

- This uses seven bits to code 128characters

- Binary codes are required since registers can hold binary informationonly

IFT YOUR LIGHT SHIPE

| Character | Binary<br>code | Character | Binary<br>code |

|-----------|----------------|-----------|----------------|

| A         | 100 0001       | 0         | 011 0000       |

| В         | 100 0010       | 1         | 011 0001       |

| С         | 100 0011       | 2         | 011 0010       |

| D         | 100 0100       | 3         | 011 0011       |

| E         | 100 0101       | 4         | 011 0100       |

| F         | 100 0110       | 5         | 011 0101       |

| G         | 100 0111       | 6         | 011 0110       |

| н         | 100 1000       | 7         | 011 0111       |

| I         | 100 1001       | 8         | 011 1000       |

| J         | 100 1010       | 9         | 011 1001       |

| K         | 100 1011       |           |                |

| L         | 100 1100       |           |                |

| Μ         | 100 1101       | space     | 010 0000       |

| N         | 100 1110       |           | 010 1110       |

| 0         | 100 1111       | (         | 010 1000       |

| Р         | 101 0000       | +         | 010 1011       |

| Q         | 101 0001       | \$        | 010 0100       |

| R         | 101 0010       | *         | 010 1010       |

| S         | 101 0011       | )         | 010 1001       |

| Т         | 101 0100       |           | 010 1101       |

| U         | 101 0101       | 1         | 010 1111       |

| V         | 101 0110       | ,         | 010 1100       |

| w         | 101 0111       | =         | 011 1101       |

| x         | 101 1000       |           |                |

| Y         | 101 1001       |           |                |

| Z         | 101 1010       |           |                |

TABLE 3-4 American Standard Code for Information Interchange (ASCII)

- Section 3.2 Complements

Complements Complements are used in digital computers for simplifying subtraction and logical ٠ manipulation

- Two types of complements for each base r system: r's complement and (r-1)'s complement

- Given a number N in base r having n digits, the (r-1)'s complement of N is • defined as  $(r^n - 1) - N$

- For decimal, the 9's complement of N is  $(10^n 1) N$ ٠

- The 9's complement of 546700 is 999999 546700 = 453299 •

- The 9's complement of 453299 is 999999 453299 = 546700

- For binary, the 1's complement of N is  $(2^n 1) N$

- The 1's complement of 1011001 is 1111111 1011001 = 0100110

- The 1's complement is the true complement of the number just toggle allbits

- The r's complement of an n-digit number N in base r is defined as  $r^n N$

- This is the same as adding 1 to the (r-1)'s complement

- The 10's complement of 2389 is 7610 + 1 = 7611

- The 2's complement of 101100 is 010011 + 1 = 010100

- Subtraction of unsigned *n*-digit numbers: *M*-*N*

- Add *M* to the *r*'s complement of *N* this results  $M + (r^n - N) = M - N + r^n$

- If  $M \ge N$ , the sum will produce an end carry  $r^n$  which is discarded

- If M < N, the sum does not produce an end carry and is equal to  $r^n (N M)$ , which is the *r*'s complement of (N M). To obtain the answer in a familiar form, take the *r*'s complement of the sum and place a negative sign in front.

Example: 72532 – 13250 = 59282. The 10's complement of 13250 is 86750.

| М                    | = 72352    |

|----------------------|------------|

| 10's comp.ofN        | <u>=</u>   |

| <u>+86750</u> Sum    | = 159282   |

| Discardendcarry      | <u>= -</u> |

| <u>100000</u> Answer | = 59282    |

|                      |            |

Example for M < N: 13250 – 72532 = -59282

| М             | = 13250                        |

|---------------|--------------------------------|

| 10's comp.ofN |                                |

| +27468Sum     | =40718                         |

| No end carry  | 24                             |

| Answer        | = -59282 (10's comp. of 40718) |

| - C/ JJ D-    | A A AN THE CONTRACTOR          |

Example for X = 1010100 and Y = 1000011

| Х                 | =1010100           |

|-------------------|--------------------|

| 2's comp. of Y    | =+0111101          |

| Sum               | = 10010001         |

| Discard end carry | <u>= -10000000</u> |

| Answer X – Y      | = 0010001          |

|                   |                    |

| Y                 | = 1000011          |

| 2's comp. of X    | =+0101100          |

| Sum               | = 1101111          |

|                   |                    |

No end carry Answer = -0010001 (2's comp. of1101111)

#### Section 3.3 – Fixed-Point Representation

- Positive integers and zero can be represented by unsignednumbers

- Negative numbers must be represented by signed numbers since + and signs are not available, only 1's and 0's are

- Signed numbers have msb as 0 for positive and 1 for negative msb is the signbit

- Two ways to designate binary point position in aregister

- Fixed pointposition

- Floating-point representation

- Fixed point position usually uses one of the two followingpositions

- A binary point in the extreme left of the register to make it afraction

- A binary point in the extreme right of the register to make it aninteger

- In both cases, a binary point is not actually present

- The floating-point representations uses a second register to designate the position of the binary point in the firstregister

- When an integer is positive, the msb, or sign bit, is 0 and the remaining bits represent themagnitude

- When an integer is negative, the msb, or sign bit, is 1, but the rest of the number can be represented in one of threeways

- Signed-magnituderepresentation

- Signed-1's complementrepresentation

- Signed-2's complementrepresentation

- Consider an 8-bit register and the number+14

- The only way to represent it is00001110

- Consider an 8-bit register and the number–14

- Signedmagnitude: 1 0001110

- Signed1'scomplement: 1 1110001

- Signed2'scomplement: 1 1110010

- Typically use signed 2'scomplement

- Addition of two signed-magnitude numbers follow the normalrules

- If same signs, add the two magnitudes and use the commonsign

- Differing signs, subtract the smaller from the larger and use the sign of the largermagnitude

- Must compare the signs and magnitudes and then either add orsubtract

- Addition of two signed 2's complement numbers does not require a comparison or subtraction only addition and complementation

- Add the two numbers, including their signbits

- Discard any carry out of the sign bitposition

- All negative numbers must be in the 2's complementform

- If the sum obtained is negative, then it is in 2's complementform

| +6  | 00000110 | -6  | 11111010 |

|-----|----------|-----|----------|

| +13 | 00001101 | +13 | 00001101 |

| +19 | 00010011 | +7  | 00000111 |

|     |          |     |          |

| +6  | 00000110 | -6  | 11111010 |

| -13 | 11110011 | -13 | 11110011 |

| -7  | 11111001 | -19 | 11101101 |

|     |          |     |          |

- Subtraction of two signed 2's complement numbers is asfollows

- Take the 2's complement form of the subtrahend (including signbit)

- Add it to the minuend (including the signbit)

- A carry out of the sign bit position is discarded

- An overflow occurs when two numbers of n digits each are added and the sum occupies n + 1 digits

- Overflows are problems since the width of a register isfinite

- Therefore, a flag is set if this occurs and can be checked by theuser

- Detection of an overflow depends on if the numbers are signed orunsigned

- For unsigned numbers, an overflow is detected from the end carry out of themsb

- For addition of signed numbers, an overflow cannot occur if one is positive and one is negative both have to have the samesign

- An overflow can be detected if the carry into the sign bit position and the carry out of the sign bit position are notequal

| +70  | 0 1000110 | -70 1 0111010  |

|------|-----------|----------------|

| +80  | 0 1010000 | -80 1 0110000  |

| +150 | 1 0010110 | -150 0 1101010 |

- The representation of decimal numbers in registers is a function of the binary code used to represent a decimaldigit

- A 4-bit decimal code requires four flip-flops for each decimaldigit

- This takes much more space than the equivalent binary representation and the circuits required to perform decimal arithmetic are more complex

- Representation of signed decimal numbers in BCD is similar to the representation of signed numbers in binary

- Either signed magnitude or signed complementsystems

- The sign of a number is represented with fourbits

- 0000 for +

- 1001 for –

- To obtain the 10's complement of a BCD number, first take the 9's complement and then add one to the least significant digit

- Example: (+375) + (-240) = +135

| 0 375  | (0000 0011 01111010) <sub>BCD</sub> |

|--------|-------------------------------------|

| +9 760 | (1001 0111 01100000) <sub>BCD</sub> |

| 0 135  | (0000 0001 00110101) <sub>BCD</sub> |

#### **Section 3.4 – Floating-Point Representation**

- The floating-point representation of a number has twoparts

- The first part represents a signed, fixed-point number the mantissa

- The second part designates the position of the binary point the *exponent*

- The mantissa may be a fraction or aninteger

- Example: the decimal number +6132.789is

- oFraction: +0.6123789

- $\circ$  Exponent: +04

- Equivalent to  $+0.6132789 \times 10^{+4}$

- A floating-point number is always interpreted to represent  $m xr^e$

- Example: the binary number +1001.11 (with 8-bit fraction and 6-bitexponent)

- Fraction: 01001110

- Exponent: 000100

- Equivalent to +(.1001110)<sub>2</sub>  $x2^{+4}$

- A floating-point number is said to be *normalized* if the most significant digit of the mantissa isnonzero

- The decimal number 350 is normalized, 00350 isnot

- The 8-bit number 00011010 is notnormalized

- Normalize it by fraction = 11010000 and exponent =-3

- Normalized numbers provide the maximum possible precision for the floatingpointnumber

#### **Section 3.5 – Other Binary Codes**

- Digital systems can process data in discrete formonly

- Continuous, or analog, information is converted into digital form by means of an analog-to-digital converter

- The reflected binary or *Gray code*, is sometimes used for the converted digital data

- The Gray code changes by only one bit as it sequences from one number to the next

- Gray code counters are sometimes used to provide the timing sequences that control the operations in a digital system

| Binary<br>code | Decimal equivalent | Binary<br>code | Decimal<br>equivalent |

|----------------|--------------------|----------------|-----------------------|

| 0000           | 0                  | 1100           | 8                     |

| 0001           | 1                  | 1101           | 9                     |

| 0011           | 2                  | 1111           | 10                    |

| 0010           | 3                  | 1110           | 11                    |

| 0110           | 4                  | 1010           | 12                    |

| 0111           | 5                  | 1011           | 13                    |

| 0101           | 6                  | 1001           | 14                    |

| 0100           | 7                  | 1000           | 15                    |

TABLE 3-5 4-Bit Gray Code

• Binary codes for decimal digits require a minimum of fourbits

• Other codes besides BCD exist to represent decimaldigits

TABLE 3-6 Four Different Binary Codes for the Decimal Digit

| Decimal<br>digit | BCD<br>8421 | 2421 | Excess-3 | Excess-3<br>gray |

|------------------|-------------|------|----------|------------------|

| 0                | 0000        | 0000 | 0011     | 0010             |

| 1                | 0001        | 0001 | 0100     | 0110             |

| 2                | 0010        | 0010 | 0101     | 0111             |

| 3                | 0011        | 0011 | 0110     | 0101             |

| 4                | 0100        | 0100 | 0111     | 0100             |

| 5                | 0101        | 1011 | 1000     | 1100             |

| 6                | 0110        | 1100 | 1001     | 1101             |

| 7                | 0111        | 1101 | 1010     | 1111             |

| 8                | 1000        | 1110 | 1011     | 1110             |

| 9                | 1001        | 1111 | 1100     | 1010             |

|                  | 1010        | 0101 | 0000     | 0000             |

| Unused           | 1011        | 0110 | 0001     | 0001             |

| bit              | 1100        | 0111 | 0010     | 0011             |

| combi-           | 1101        | 1000 | 1101     | 1000             |

| nations          | 1110        | 1001 | 1110     | 1001             |

|                  | 1111        | 1010 | 1111     | 1011             |

- The 2421 code and the excess-3 code are both*self-complementing*

- The 9's complement of each digit is obtained by complementing each bit in the code

- The 2421 code is a *weightedcode*

- The bits are multiplied by indicated weights and the sum gives the decimaldigit

- The excess-3 code is obtained from the corresponding BCD code added to3

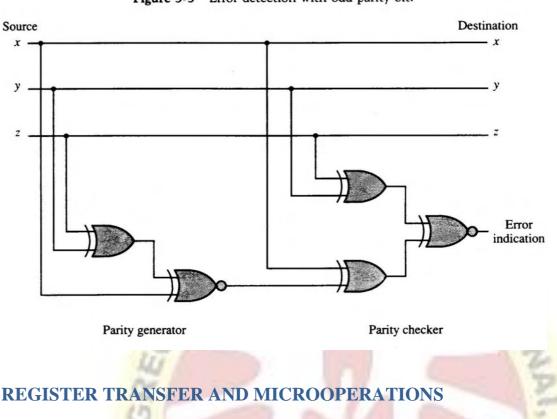

#### **Section 3.6 – Error Detection Codes**

10

- Transmitted binary information is subject to noise that could change bits 1 to 0 and vice versa

- An *error detection code* is a binary code that detects digital errors during transmission

- The detected errors cannot be corrected, but can prompt the data tobe retransmitted

- The most common error detection code used is the *paritybit*

- A parity bit is an extra bit included with a binary message to make the total number of 1's either odd oreven

| TABLE 3.       | 7 Parity Bit | Generatior |

|----------------|--------------|------------|

| Message<br>xyz | P(odd)       | P(even)    |

| 000            | 1            | 0          |

| 001            | 0            | 1          |

| 010            | 0            | 1          |

| 011            | 1            | 0          |

| 100            | 0            | 1          |

| 101            | 1            | 0          |

| 110            | 1            | 0          |

| 111            | 0            | 1          |

- The P(odd) bit is chosen to make the sum of 1's in all four bitsodd

- The even-parity scheme has the disadvantage of having a bit combination of all 0's

- Procedure duringtransmission:

- At the sending end, the message is applied to a *paritygenerator*

- The message, including the parity bit, istransmitted

- At the receiving end, all the incoming bits are applied to a *paritychecker*

- Any odd number of errors are detected

- Parity generators and checkers are constructed with XOR gates (oddfunction)

- An odd function generates 1 iff an odd number if input variables are1

Figure 3-3 Error detection with odd parity bit.

- ✓ Register TransferLanguage

- ✓ RegisterTransfer

- ✓ Bus And MemoryTransfers

- ✓ Types of Micro-operations

- ✓ ArithmeticMicro-operations

- ✓ LogicMicro-operations

- ✓ ShiftMicro-operations

- ✓ Arithmetic Logic ShiftUnit

#### **BASIC DEFINITIONS:**

> A digital system is an interconnection of digital hardwaremodules.

Ygu

- > The modules are registers, decoders, arithmetic elements, and controllogic.

- The various modules are interconnected with common data and control paths to form a digital computer system.

SHIH

- Digital modules are best defined by the registers they contain and the operations that are performed on the data stored in them.

- > The operations executed on data stored in registers are called *microoperations*.

- A *microoperation* is an elementary operation performed on the information stored in one or more registers.

- The result of the operation may replace the previous binary information of a register or may be transferred to another register.

- > Examples of microoperations are shift, count, clear, andload.

- The internal hardware organization of a digital computer is best defined byspecifying:

- 1. The set of registers it contains and theirfunction.

- 2. The sequence of microoperations performed on the binary information stored in theregisters.

- **3**. The control that initiates the sequence of microoperations.

# **REGISTER TRANSFER LANGUAGE:**

- The symbolic notation used to describe the micro-operation transfer among registers is called RTL (Register TransferLanguage).

- The use of *symbols* instead of a *narrative explanation* provides an organized and concise manner for listing the micro-operation sequences in registers and the control functions that initiatethem.

- A register transfer language is a system for expressing in symbolic form the microoperation sequences among the registers of a digitalmodule.

- It is a convenient tool for describing the internal organization of digital computers in concise and precise manner.

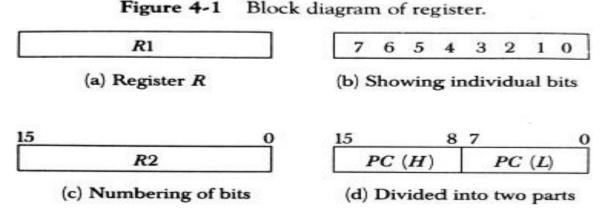

## **Registers:**

- Computer registers are designated by upper case letters (and optionally followed by digits or letters) to denote the function of theregister.

- ➢ For example, the register that holds an address for the memory unit is usually called a memory address register and is designated by the nameMAR.

- > Other designations for registers are PC (for program counter), IR (for instruction register, and R1 (for processor register).

- The individual flip-flops in an n-bit register are numbered in sequence from 0 through n-1, starting from 0 in the rightmost position and increasing the numbers toward theleft.

- ▶ Figure 4-1 shows the representation of registers in block diagramform.

- The most common way to represent a register is by a rectangular box with the name of the register inside, as in Fig.4-1(a).

- > The individual bits can be distinguished as in(b).

- > The numbering of bits in a 16-bit register can be marked on top of the box as shown in(c).

- 16-bitregisterispartitionedintotwopartsin (d).Bits0through7areassignedthesymbolL(for low byte) and bits 8 through 15 are assigned the symbol H (for highbyte).

- The name of the 16-bit register is *PC*. The symbol *PC* (0-7) or *PC* (*L*) refers to the low-order byte and PC (8-15) or *PC* (*H*) to the high-orderbyte.

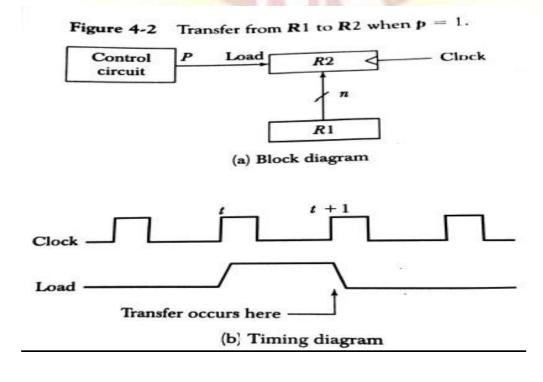

## **Register Transfer:**

- Information transfer from one register to another is designated in symbolic form by means of a replacement operator.

- > The statement  $R2 \leftarrow R1$  denotes a transfer of the content of register R1 into register R2.

- > It designates a replacement of the content of R2 by the content of R1.

- > By definition, the content of the source register R 1 does not change after the transfer.

- If we want the transfer to occur only under a predetermined control condition then it can be shown by an if-thenstatement.

# if (P=1) then R2← R1

- > P is the control signal generated by a control section.

- We can separate the control variables from the register transfer operation by specifying a *Control Function*.

- Control function is a Boolean variable that is equal to 0 or 1.

- control function is included in the statementas

#### **P: R2← R1**

- Control condition is terminated by a colon implies transfer operation be executed by the hardware only ifP=1.

- Every statement written in a register transfer notation implies a hardware construction for implementing thetransfer.

- Figure 4-2 shows the block diagram that depicts the transfer from R1 toR2.

- > The n outputs of register R1 are connected to the n inputs of register R2.

- The letter n will be used to indicate any number of bits for the register. It will be replaced by an actual number when the length of the register isknown.

- > Register R2 has a load input that is activated by the control variableP.

- It is assumed that the control variable is synchronized with the same clock as the one applied to theregister.

- As shown in the timing diagram, P is activated in the control section by the rising edge of a clock pulse at timet.

- > The next positive transition of the clock at time t + 1 finds the load input active and the data inputs of R2 are then loaded into the register in parallel.

- > P may go back to 0 at time t+1; otherwise, the transfer will occur with every clock pulse transition while P remainsactive.

- Even though the control condition such as P becomes active just after time t, the actual transfer doesnotoccuruntiltheregisteristriggeredbythenext positivetransitionoftheclockattime t+1.

| Symbol                | Description                     | Examples         |

|-----------------------|---------------------------------|------------------|

| Letters(and numerals) | Denotes a register              | MAR, R2          |

| Parentheses ()        | Denotes a part of a register    | R2(0-7), R2(L)   |

| Arrow <               | Denotes transfer of information | R2 < R1          |

| Comma ,               | Separates two microoperations   | R2 < R1, R1 < R2 |

> The basic symbols of the register transfer notation are listed in belowtable

> A comma is used to separate two or more operations that are executed at the sametime.

> Thestatement

#### $T:R2 \leftarrow R1, R1 \leftarrow R2$ (exchangeoperation)

denotes an operation that exchanges the contents of two rgisters during one common clock pulse provided that T=1.

#### **Bus and Memory Transfers:**

- A more efficient scheme for transferring information between registers in *a multiple-register configuration* is a *Common BusSystem*.

- A common bus consists of a set of common lines, one for each bit of aregister.

- > Controlsignalsdeterminewhichregisterisselectedbythebusduringeachparticularregister transfer.

- Different ways of constructing a Common BusSystem

- ✓ UsingMultiplexers

- ✓ Using Tri-state Buffers

# **Common bus system is with multiplexers:**

The multiplexers select the source register whose binary information is then placed on thebus.

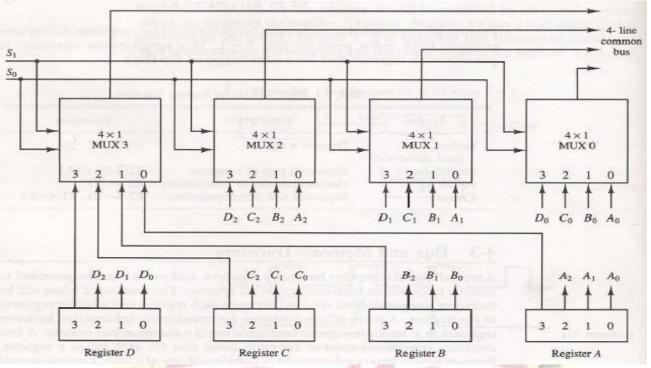

> The construction of a bus system for four registers is shown in belowFigure.

- The bus consists of four 4 x 1 multiplexers each having four data inputs, 0 through 3, and two selection inputs, S<sub>1</sub> and S<sub>0</sub>.

- For example, output 1 of register A is connected to input 0 of MUX 1 because this input is labelled A<sub>1</sub>.

- The diagram shows that the bits in the same significant position in each register are connected to the data inputs of one multiplexer to form one line of thebus.

- Thus MUX 0 multiplexes the four 0 bits of the registers, MUX 1 multiplexes the four 1 bits of the registers, and similarly for the other twobits.

- > The two selection lines Si and So are connected to the selection inputs of all fourmultiplexers.

- The selection lines choose the four bits of one register and transfer them into the four-line commonbus.

- > When  $S_1S_0 = 00$ , the 0 data inputs of all four multiplexers are selected and applied to the outputs that form thebus.

- This causes the bus lines to receive the content of register A since the outputs of this register are connected to the 0 data inputs of themultiplexers.

- Similarly, register *B* is selected if  $S_1S_0 = 01$ , and soon.

- Table 4-2 shows the register that is selected by the bus for each of the four possible binary value of the selectionlines.

| $S_1$ | S <sub>0</sub> | Register selected |

|-------|----------------|-------------------|

| 0     | 0              | Α                 |

| 0     | 1              | В                 |

| 1     | 0              | С                 |

| 1     | 1              | D                 |

- ➤ In general a bus systemhas

- ✓ multiplex "k"Registers

- ✓ eachregisterof"n"bits

- ✓ toproduce"n-linebus"

- no. of multiplexers required =n

- $\checkmark$  size of each multiplexer = k x 1

- > When the bus is includes in the statement, the register transfer is symbolized asfollows:

# BUS← C, R1← BUS

The content of register C is placed on the bus, and the content of the bus is loaded into register R1 by activating its load control input. If the bus is known to exist in the system, it may be convenient just to show the directtransfer.

#### **R1← C**

# Three-State Bus Buffers:

- > A bus system can be constructed with three-state gates instead of multiplexers.

- A three-state gate is a digital circuit that exhibits threestates.

- > Two of the states are signals equivalent to logic 1 and 0 as in a conventional gate.

- > The third state is a *high-impedancestate*.

- > The high-impedance state behaves like an open circuit, which means that the output is disconnected and does not have logicsignificance.

- > Becauseofthisfeature, a largenumber of three-stategate outputs can be connected with wires toformacommonbuslinewithoutendangeringloadingeffects.

- > The graphic symbol of a three-state buffer gate is shown in Fig.4-4.

# Figure 4-4 Graphic symbols for three-state buffer.

# Control input C

- > It is distinguished from a normal buffer by having both a normal input and a controlinput.

- > The control input determines the output state. When the control input is equal to 1, the output is enabled and the gate behaves like any conventional buffer, with the output equal to the normal input.

- > When the control input is 0, the output is disabled and the gate goes to a high-impedance state, regardless of the value in the normalinput.

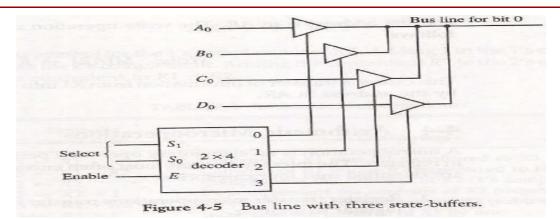

- The construction of a bus system with three-state buffers is shown in Fig.4

- > The outputs of four buffers are connected together to form a single busline.

- The control inputs to the buffers determine which of the four normal inputs will communicate with the busline.

- No more than one buffer may be in the active state at any given time. The connected buffers must be controlled so that only one three-state buffer has access to the bus line while all other buffers are maintained in a high impedancestate.

- One way to ensure that no more than one control input is active at any given time is to use a decoder, as shown in thediagram.

- When the enable input of the decoder is 0, all of its four outputs are 0, and the bus line is in a high-impedance state because all four buffers are disabled.

- When the enable input is active, one of the three-state buffers will be active, depending on the binary value in the select inputs of thedecoder.

## Memory Transfer:

> The transfer of information from a memory word to the outside environment is called a*read* operation.

- > The transfer of new information to be stored into the memory is called a *write*operation.

- A memory word will be symbolized by the letterM.

- The particular memory word among the many available is selected by the memory address during thetransfer.

- > It is necessary to specify the address of M when writing memory transferoperations.

- > This will be done by enclosing the address in square brackets following the letterM.

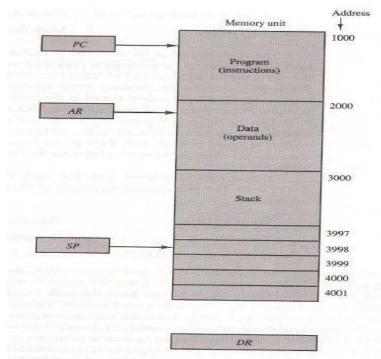

- Consider a memory unit that receives the address from a register, called the address register, symbolized byAR.

- > The data are transferred to another register, called the data register, symbolized byDR.

- > The read operation can be stated asfollows:

# Read: DR<- M [AR]

- This causes a transfer of information into DR from the memory word M selected by the address in AR.

- The write operation transfers the content of a data register to a memory word M selected by the address. Assume that the input data are in register R1 and the address is inAR.

- > The write operation can be stated asfollows:

# Write: M [AR] <- R1

# Types of Micro-operations:

*<u>Register Transfer Micro-operations:</u>*Transfer binary information from one register toanother.

- > <u>Arithmetic Micro-operations:</u>Perform arithmetic operation on numeric data stored inregisters.

- > <u>Logical Micro-operations</u>: Perform bit manipulation operations on data stored inregisters.

- Shift Micro-operations: Perform shift operations on data stored inregisters.

- RegisterTransferMicro-operationdoesn'tchangetheinformationcontentwhenthebinary information moves from source register to destinationregister.

- Other three types of micro-operations change the information change the information content during thetransfer.

#### **Arithmetic Micro-operations:**

- The basic arithmetic micro-operationsare

- $\circ$  Addition

- o Subtraction

- o Increment

- Decrement

- o Shift

- The arithmetic Micro-operation defined by the statement below specifies the add micro-operation.

## **R3** ← **R1** + **R2**

- > It states that the contents of R1 are added to contents of R2 and sum is transferred toR3.

- To implement this statement hardware requires 3 registers and digital component that performs addition

- Subtraction is most often implemented through complementation and addition.

- > The subtract operation is specified by the followingstatement

## $R3 \leftarrow R1 + R2 + 1$

- > instead of minus operator, we can write as

- R2isthesymbolforthe1'scomplementofR2

- > Adding1to1'scomplementproduces2'scomplement

- > Addingthecontentsof*R1*tothe2'scomplementofR2isequivalenttoR1-R2.

# **Binary Adder:**

- > Digitalcircuitthatformsthearithmeticsumof2bitsandthepreviouscarryiscalledFULLADDER.

- Digital circuit that generates the arithmetic sum of 2 binary numbers of any lengths iscalled BINARY ADDER.

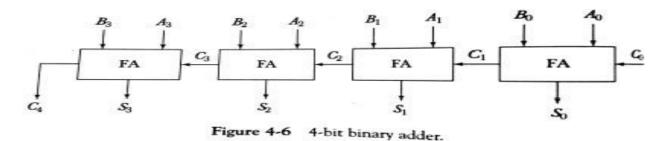

- Figure 4-6 shows the interconnections of four full-adders (FA) to provide a 4-bit binaryadder.

> The augends bits of A and the addend bits of *B* are designated by subscript numbers from

right to left, with subscript 0 denoting the low-orderbit.

- The carries are connected in a chain through the full-adders. The input carry to the binaryadderisCoandtheoutputcarryisC4. The Soutputsofthefull-addersgenerate the required sumbits.

- > An n-bit binary adder requires nfull-adders.

# **Binary Adder – Subtractor:**

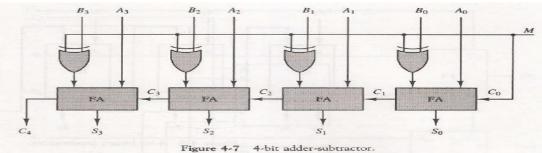

- The addition and subtraction operations can be combined into one common circuit by includingan exclusive-OR gate with eachfull-adder.

- ➤ A 4-bit adder-subtractor circuit is shown in Fig.4-7.

- > The mode input M controls the operation. When M = 0 the circuit is an adder and when M = 1 the circuit becomes a ubtractor.

- Each exclusive-OR gate receives input M and one of the inputs of B

- When M = 0, we have B xor 0 = B. The full-adders receive the value of B, the input carry is 0, and the circuit performs A plusB.

- When M = 1, we have B x or 1 = B' and Co = 1.

- $\succ$  The *B* inputs are all complemented and a 1 is added through the input arry.

- > The circuit performs the operation A plus the 2's complement of *B*.

# **Binary Incrementer:**

- > The increment microoperation adds one to a number in aregister.

- > For example, if a 4-bit register has a binary value 0110, it will go to 0111 after it isincremented.

- > This can be accomplished by means of half-adders connected incascade.

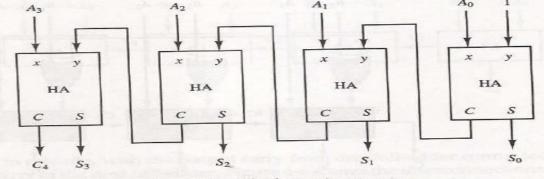

- > The diagram of a 4-bit 'combinational circuit incrementer is shown in Fig.4-8.

Figure 4-8 4-bit binary incrementer.

- One of the inputs to the least significant half-adder (HA) is connected to logic-1 and the other input is connected to the least significant bit of the number to beincremented.

- The output carry from one half-adder is connected to one of the inputs of the next-higher-order half-adder.

- The circuit receives the four bits from A<sub>0</sub> through A<sub>3</sub>, adds one to it, and generates the incremented output in S<sub>0</sub> throughS<sub>3</sub>.

- > The output carry  $C_4$  will be 1 only after incrementing binary 1111. This also causes outputs S<sub>0</sub> through S<sub>3</sub> to go to0.

- The circuit of Fig. 4-8 can be extended to an *n* -bit binary incrementer by extending the diagram to include *n*half-adders.

- The least significant bit must have one input connected to logic-1. The other inputs receive the number to be incremented or the carry from the previousstage.

#### Arithmetic Circuit:

- > The basic component of an arithmetic circuit is the paralleladder.

- By controlling the data inputs to the adder, it is possible to obtain different types of arithmetic operations.

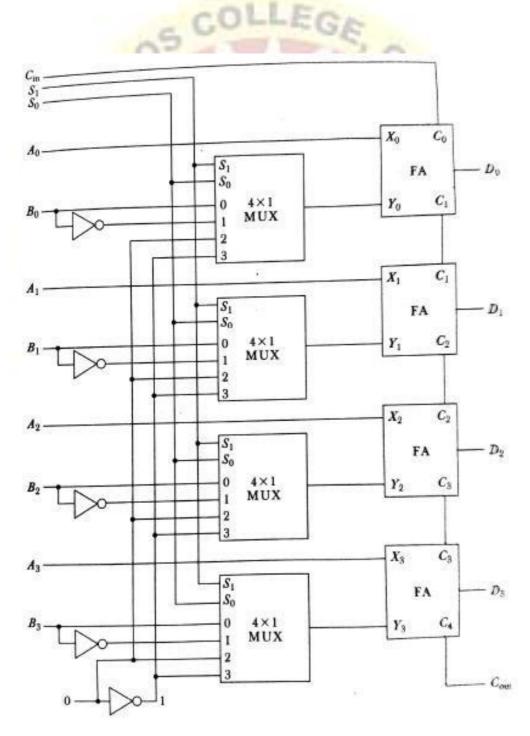

- The diagram of a 4-bit arithmetic circuit is shown in Fig. 4-9. It has four full-adder circuits that constitute the 4-bit adder and four multiplexers for choosing different perations.

- There are two 4-bit inputs A and *B* and a 4-bit output*D*.

- > The four inputs from A go directly to the X inputs of the binaryadder.

- Each of the four inputs from B are connected to the data inputs of themultiplexers.

- > The multiplexers data inputs also receive the complement of B.

- > The other two data inputs are connected to logic-0 andlogic-1.

- > The four multiplexers are controlled by two selection inputs  $S_1$  and  $S_0$ . The input carry  $C_{in}$ , goes to the carry input of the FA in the least significant position. The other carries are connected from one stage to thenext.

- > By controlling the value of Y with the two selection inputs  $S_1$  and  $S_0$  and making  $C_{in}$  equal to 0 or 1, it is possible to generate the eight arithmetic microoperations listed in Table44.

| Select<br>S <sub>1</sub> S <sub>0</sub> C <sub>in</sub> |   |            |                                                                           |                            |                      |

|---------------------------------------------------------|---|------------|---------------------------------------------------------------------------|----------------------------|----------------------|

|                                                         |   | Input<br>Y | $\begin{array}{l} \text{Output} \\ D = A + Y + C_{\text{in}} \end{array}$ | Microoperation             |                      |

| 0                                                       | 0 | 0          | B                                                                         | D = A + B                  | Add                  |

| 0                                                       | 0 | 1          | B                                                                         | D = A + B + 1              | Add with carry       |

| 0                                                       | 1 | 0          | B                                                                         | $D = A + \overline{B}$     | Subtract with borrow |

| 0                                                       | 1 | 1          | B                                                                         | $D = A + \overline{B} + 1$ | Subtract             |

| 1                                                       | Ō | 0          | 0                                                                         | D = A                      | Transfer A           |

| 1                                                       | 0 | 1          | 0                                                                         | D = A + 1                  | Increment A          |

| 1                                                       | 1 | 0          | 1                                                                         | D = A - 1                  | Decrement A          |

| 1                                                       | 1 | 1          | 1                                                                         | D = A                      | Transfer A           |

# TABLE 4-4 Arithmetic Circuit Function Table

#### Addition:

- > When  $S_1S_0 = 00$ , the value of *B* is applied to the Y inputs of theadder.

- ✓ If Cir, = 0, the output D=A+B.

- ✓ If Cin = 1, output D = A + B + 1.

- > Both cases perform the add microoperation with or without adding the inputcarry.

#### Subtraction:

- > When  $S_1S_0 = 01$ , the complement of B is applied to the Y inputs of theadder.

- ✓ If  $C_{in} = 1$ , then D = A + B + 1. This produces A plus the 2's complement of B, which is equivalent to a subtraction of A-B.

- ✓ When  $C_{in} = 0$  then D = A + B. This is equivalent to a subtract with borrow, that is, A-B-1.

#### Increment:

- When  $S_1S_0 = 10$ , the inputs from *B* are neglected, and instead, all 0's are inserted into the Y inputs. The output becomes  $D = A + 0 + C_{in}$ . This gives D = A when  $C_{in} = 0$  and D = A + 1 when  $C_{in} = 1$ .

- ▶ In the first case we have a direct transfer from input A to outputD.

- ➤ In the second case, the value of A is incremented by1.

#### **Decrement:**

- → When  $S_1S_0=11$ , all l's are inserted into the Y inputs of the adder to produce the decrement operation D = A 1 when  $C_{in} = 0$ .

- This is because a number with all 1's is equal to the 2's complement of 1 (the 2's complement of binary 0001 is 1111). Adding a number A to the 2's complement of 1 produces F = A + 2's complementof1=A—1.WhenC<sub>in</sub>=1,thenD=A -1+1=A,whichcausesadirecttransferfrom input A to output D.

#### Logic Micro-operations:

- > Logic microoperations specify binary operations for strings of bits stored inregisters.

- > These operations consider each bit of the register separately and treat them as binaryvariables.

- For example, the exclusive-OR microoperation with the contents of two registers RI and R2 is symbolized by thestatement

$$P: R1 \leftarrow R1 \oplus R2$$

It specifies a logic microoperation to be executed on the individual bits of the registers provided that the control variable P =1.

## List of Logic Microoperations:

- > There are 16 different logic operations that can be performed with two binaryvariables.

- They can be determined from all possible truth tables obtained with two binary variables as shown in Table4-5.

| x | у | $F_0$ | $F_1$ | $F_2$ | $F_3$ | $F_4$ | $F_5$ | $F_6$ | <i>F</i> <sub>7</sub> | $F_8$ | <i>F</i> <sub>9</sub> | <i>F</i> <sub>10</sub> | <i>F</i> <sub>11</sub> | <i>F</i> <sub>12</sub> | <i>F</i> <sub>13</sub> | <i>F</i> <sub>14</sub> | $F_{15}$ |

|---|---|-------|-------|-------|-------|-------|-------|-------|-----------------------|-------|-----------------------|------------------------|------------------------|------------------------|------------------------|------------------------|----------|

| 0 | 0 | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0                     | 1     | 1                     | 1                      | 1                      | 1                      | 1                      | 1                      | 1        |

|   |   |       |       |       |       |       |       |       |                       |       |                       |                        |                        |                        |                        | 1                      |          |

| 1 | 0 | 0     | 0     | 1     | 1     | 0     | 0     | 1     | 1                     | 0     | 0                     | 1                      | 1                      | 0                      | 0                      | 1                      | 1        |

|   |   |       |       |       |       |       |       |       |                       |       |                       |                        |                        |                        |                        | 0                      | 1        |

TABLE 4-5 Truth Tables for 16 Functions of Two Variables

- The 16 Boolean functions of two variables x and y are expressed in algebraic form in the first column of Table4-6.

- The 16 logic microoperations are derived from these functions by replacing variable x by the binary content of register A and variable y by the binary content of registerB.

- The logic micro-operations listed in the second column represent a relationship between the binary content of two registers A andB.

| Boolean function         | Microoperation                                               | Name           |

|--------------------------|--------------------------------------------------------------|----------------|

| $F_0 = 0$                | <i>F</i> ← 0                                                 | Clear          |

| $F_1 = xy$ $F_2 = xy'$   | $F \leftarrow A \land B$ $F \leftarrow A \land \overline{B}$ | AND            |

| $F_3 = x$<br>$F_4 = x'y$ | $F \leftarrow A \\ F \leftarrow \overline{A} \land B$        | Transfer A     |

| $F_5 = y$                | $F \leftarrow B$                                             | Transfer B     |

| $F_6 = x \oplus y$       | $F \leftarrow A \oplus B$                                    | Exclusive-OR   |

| $F_7 = x + y$            | $F \leftarrow A \lor B$                                      | OR             |

| $F_8 = (x + y)'$         | $F \leftarrow \overline{A \lor B}$                           | NOR            |

| $F_9 = (x \oplus y)'$    | $F \leftarrow \overline{A \oplus B}$                         | Exclusive-NOR  |

| $F_{10} = y'$            | $F \leftarrow \overline{B}$                                  | Complement B   |

| $F_{11} = x + y'$        | $F \leftarrow A \lor \overline{B}$                           |                |

| $F_{12} = x'$            | $F \leftarrow \overline{A}$                                  | Complement A   |

| $F_{13} = x' + y$        | $F \leftarrow \overline{A} \lor B$                           |                |

| $F_{14} = (xy)'$         | $F \leftarrow \overline{A \land B}$                          | NAND           |

| $F_{15} = 1$             | $F \leftarrow all 1$ 's                                      | Set to all 1's |

# Hardware Implementation:

LU.

- The hardware implementation of logic microoperations requires that logic gates be inserted for each bit or pair of bits in the registers to perform the required logicfunction.

- Although there are 16 logic microoperations, most computers use only four--AND, OR, XOR (exclusive-OR), and complement from which all others can bederived.

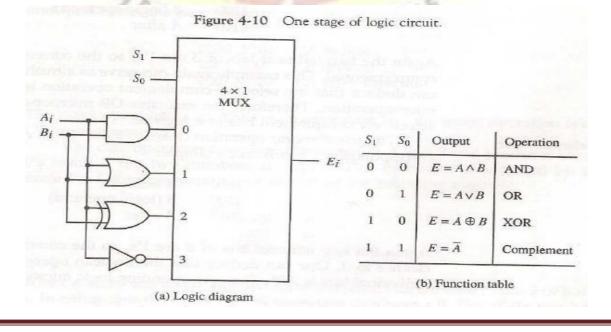

- Figure 4-10 shows one stage of a circuit that generates the four basic logicmicrooperations.

- It consists of four gates and a multiplexer. Each of the four logic operations is generated through a gate that performs the requiredlogic.

- > The outputs of the gates are applied to the data inputs of the multiplexer. The two selection inputs  $S_1$  and  $S_0$  choose one of the data inputs of the multiplexer and direct its value to the output.

#### Some Applications:

- Logic micro-operations are very useful for manipulating individual bits or a portion of a word stored in a register.

- > They can be used to change bit values, delete a group of bits or insert new bits values into aregister.

- The following example shows how the bits of one register (designated by A) are manipulated by logic microoperations as a function of the bits of another register (designated byB).

- Selectiveset

- ✓ The *selective-set* operation sets to 1 the bits in register A where there are correspondingl'sinregisterB.Itdoesnotaffectbitpositionsthathave0'sinB.Thefollowing numerical example clarifies thisoperation:

| 1010          | A before          |

|---------------|-------------------|

| 1100          | B (logic operand) |

| 1110          | A after           |

| a line of the |                   |

- ✓ The OR microoperation can be used to selectively set bits of aregister.

- Selectivecomplement

- The selective-complement operation complements bits in A where there are corresponding 1's in B. It does not affect bit positions that have 0's in B. For example:

| 1010 | A before          |

|------|-------------------|

| 1100 | B (logic operand) |

| 0110 | A after           |

The exclusive-OR microoperation can be used to selectively complement bits of aregister.

- Selectiveclear

- ✓ The *selective-clear* operation clears to 0 the bits in Aonly where there corresponding l's in B. Forexample:

| 1010 | A before          |

|------|-------------------|

| 1100 | B (logic operand) |

| 0010 | A after           |

|      |                   |

are

- The corresponding logic microoperationis

- ➢ <u>Mask</u>

- The *mask* operation is similar to the selective-clear operation except that the bits of A are cleared only where there are corresponding O's in B. The mask operation is an AND micro operation as seen from the following numerical example:

| 0110 101 | 0 A before       |   |

|----------|------------------|---|

| 0000 111 | 1 B (mask)       |   |

| 0000 101 | 0 A after maskin | g |

- ➢ Insert

- ✓ The *insert* operation inserts a new value into a group of bits. This is done by first masking the bits and then ORing them with the requiredvalue.

- ✓ For example, suppose that an A register contains eight bits, 0110 1010. To replace the four leftmost bits by the value 1001 we first mask the four unwantedbits:

| 0110 | 1010 | A before        |

|------|------|-----------------|

| 0000 | 1111 | B (mask)        |

| 0000 | 1010 | A after masking |

and then insert the new value:

| 0000 1010 | A before          |

|-----------|-------------------|

| 1001 0000 | B (insert)        |

| 1001 1010 | A after insertion |

✓ The mask operation is an AND microoperation and the insert operation is an OR microoperation.

➢ Clear

$\checkmark$  The *clear* operation compares the words in *A* and *B* and produces an all 0's result if the two numbers are equal. This operation is achieved by an exclusive-OR microoperation as shown by the followingexample

| 1010 | А                         |

|------|---------------------------|

| 1010 | В                         |

| 0000 | $A \leftarrow A \oplus B$ |

#### **Shift Microoperations:**

- > Shift microoperations are used for serial transfer ofdata.

- > The contents of a register can be shifted to the left or theright.

- > Duringashift-leftoperationtheserialinputtransfersabitintotherightmostposition.

- > Duringashift-rightoperationtheserialinputtransfersabitintotheleftmostposition.

- > There are three types of shifts: logical, circular, and arithmetic.

- The symbolic notation for the shift microoperations is shown in Table4-7. TABLE 4-7 Shift Microoperations

| Symbolic designation                | Description                     |

|-------------------------------------|---------------------------------|

| $R \leftarrow \text{shl } R$        | Shift-left register R           |

| $R \leftarrow \text{shr } R$        | Shift-right register R          |

| $R \leftarrow \text{cil } R$        | Circular shift-left register R  |

| $R \leftarrow \operatorname{cir} R$ | Circular shift-right register R |

| $R \leftarrow \text{ashl } R$       | Arithmetic shift-left R         |

| $R \leftarrow a shr R$              | Arithmetic shift-right R        |

- > LogicalShift:

- A *logical* shift is one that transfers 0 through the serialinput.

- The symbols *shl*and shr for logical shift-left and shift-rightmicrooperations.

- The microoperations that specify a 1-bit shift to the left of the content of register R and a 1-bit shift to the right of the content of register R shown in table4.7.

- $\circ$  The bit transferred to the end position through the serial input is assumed to be 0 during a logical shift.

# > CircularShift:

- The *circular* shift (also known as a *rotate* operation) circulates the bits of the register around the two ends without loss of information.

- This is accomplished by connecting the serial output of the shift register to its serialinput.

- We will use the symbols *cil*and *cir* for the circular shift left and right, respectively.

# > ArithmeticShift:

- An *arithmetic shift* is a microoperation that shifts a signed binary number to the left or right.

- An arithmetic shift-left multiplies a signed binary number by2.

- An arithmetic shift-right divides the number by2.

- Arithmetic shifts must leave the sign bit unchanged because the sign of thenumber remains the same when it is multiplied or divided by2.

| $R_{n-1}$   | $R_{n-2}$ | $R_1$ | R <sub>0</sub> |

|-------------|-----------|-------|----------------|

| Sign<br>bit |           | 1     | 1              |

# Hardware Implementation:

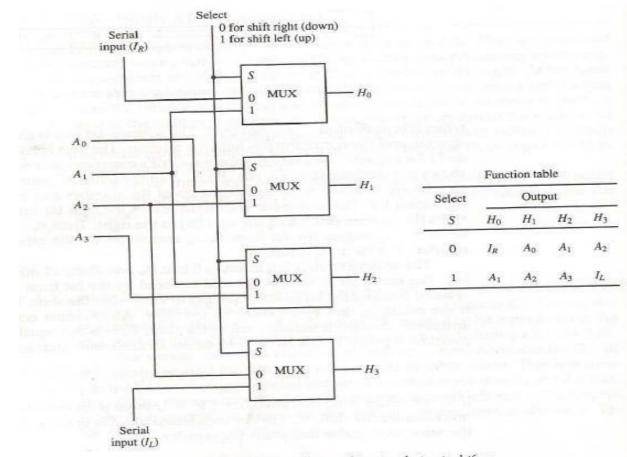

- > A combinational circuit shifter can be constructed with multiplexers as shown in Fig.4-12.

- > The4-bitshifterhasfourdatainputs,  $A_0$  through  $A_3$ , and four dataoutputs,  $H_0$  through  $H_3$ .

- > There are two serial inputs, one for shift left ( $I_L$ ) and the other for shift right( $I_R$ ).

- > When the selection input S=0 the input data are shifted right (down in the diagram).

- > When S = 1, the input data are shifted left (up in the diagram).

- > The function table in Fig. 4-12 shows which input goes to each output after theshift.

- > A shifter with n data inputs and outputs requires nmultiplexers.

- > Thetwoserialinputscanbecontrolledbyanothermultiplexertoprovidethethreepossibletypes of shifts.

Figure 4-12 4-bit combinational circuit shifter.

# Arithmetic Logic Shift Unit:

- Instead of having individual registers performing the microoperations directly, computer systems employ a number of storage registers connected to a common operational unit called an arithmetic logic unit, abbreviatedALU.

- > The ALU is a combinational circuit so that the entire register transfer operation from the

- source registers through the ALU and into the destination register can be performed during one clock pulse period.

- The shift microoperations are often performed in a separate unit, but sometimes the shift unit is made part of the overallALU.

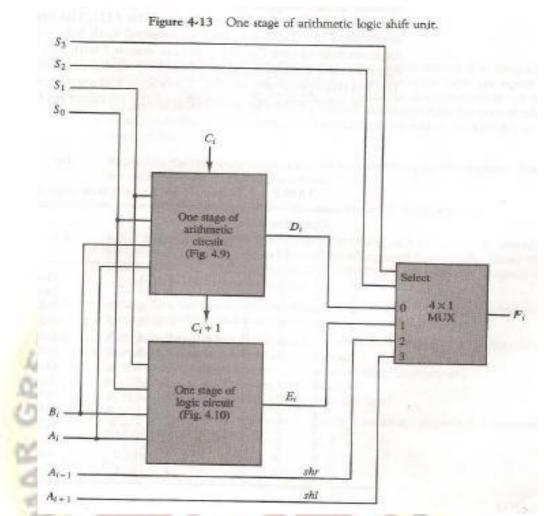

- The arithmetic, logic, and shift circuits introduced in previous sections can be combined into one ALU with common selection variables. One stage of an arithmetic logic shift unit is shown in Fig. 4-13.

- > Particular microoperation is selected with inputs  $S_1$  and  $S_0$ . A 4 x 1 multiplexer at the output chooses between an arithmetic output in  $D_i$  and a logic output in $E_i$ .

- The data in the multiplexer are selected with inputs S<sub>3</sub> and S<sub>2</sub>. The other two data inputs to the multiplexer receive inputs A<sub>i-1</sub> for the shift-right operation and A<sub>i+1</sub> for the shift-leftoperation.

- The circuit whose one stage is specified in Fig. 4-13 provides eight arithmetic operation, four logic operations, and two shiftoperations.

- $\succ$  Each operation is selected with the five variables S<sub>3</sub>, S<sub>2</sub>, S<sub>1</sub>, S<sub>0</sub> and C<sub>in</sub>.

- > The input carry  $C_{in}$  is used for selecting an arithmetic operationonly.

- > Table 4-8 lists the 14 operations of the ALU. The first eight are arithmetic operations and are selected with  $S_3S_2 = 00$ .

- > The next four are logic and are selected with  $S_3S_2 = 01$ .

- > Theinputcarryhasnoeffectduringthelogicoperationsandismarkedwithdon't-carex's.

- > The last two operations are shift operations and are selected with  $S_3S_2 = 10$  and 11.

YOUR LIGHT SH

|                            | Operation select                                                                                                                                                                          |                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|----------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Operation                  | Cin                                                                                                                                                                                       | So                                                                                                                                                                                                                                                 | $S_1$                                                                                                                                                                                                                                                                                | <i>S</i> <sub>2</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | S3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| F = A                      | 0                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| F = A + 1                  | 1                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| F = A + B                  | 0                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| F = A + B + 1              | 1                                                                                                                                                                                         | 1                                                                                                                                                                                                                                                  | 0                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $F = A + \overline{B}$     | 0                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| $F = A + \overline{B} + 1$ | 1                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                  | 1                                                                                                                                                                                                                                                                                    | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |